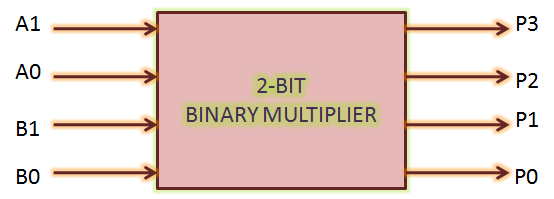

Binary Multiplier Block Diagram

Block diagram of array multiplier for 4 bit numbers Multiplier bit binary diagram block logic using gates two numbers vlsi figure multiplying Multiplier operands two multiplied shifting

A 4×4 bit array multiplier [12], [16]. | Download Scientific Diagram

Multiplier design2 Block diagram of the proposed multiplier with one parallel Binary multiplication partial sums during find multiplier bit

Design example binary multiplier. block diagram asm chart

4-bit multiplier design2[binary] how to find partial sums during multiplication? : r/mathhelp Multiplier parallel proposed correction composedBlock diagram of the multiplier: two 8-bit operands a and b are.

Solved: chapter 18 problem 17p solutionBlock diagram of an unsigned 8-bit array multiplier. Multiplier numbersMultiplier bit binary using multiplication adders schematic calculator divider digital 4x4 adder logic gates electronics electricaltechnology possible multipliers types build.

Multiplier asm chart

Binary multiplierA 4×4 bit array multiplier [12], [16]. 4 bit multiplier circuit diagramMultiplier bit unsigned.

Courses:system_design:synthesis:combinational_logic:example_of_aBinary multipliers Multiplier binaryMultiplier vhdl bit logic diagram block example courses synthesis combinational system online.

2-bit binary multiplier : vlsi n eda

Multiplier bit binary two circuit diagram block vlsiBinary multipliers Block diagram of an 8-bit multiplier.Multiplier binary logic.

2-bit binary multiplier : vlsi n edaMultiplier binary circuits multiplication bits adders technobyte Digital logicBlock diagram of binary multiplier.

Multiplier array

.

.

![A 4×4 bit array multiplier [12], [16]. | Download Scientific Diagram](https://i2.wp.com/www.researchgate.net/profile/Maaruf_Ali/publication/333968081/figure/download/fig2/AS:772998130855936@1561308524096/A-44-bit-array-multiplier-12-16.png)

Block diagram of array multiplier for 4 bit numbers | Download

Binary multipliers

2-bit binary multiplier : VLSI n EDA

Block diagram of the proposed multiplier with one parallel

![[Binary] How to find partial sums during Multiplication? : r/MathHelp](https://i2.wp.com/www.electronicshub.org/wp-content/uploads/2015/06/4-bit-binary-multiplier.jpg)

[Binary] How to find partial sums during Multiplication? : r/MathHelp

Block diagram of the multiplier: Two 8-bit operands a and b are

Multiplier - Designing of 2-bit and 3-bit binary multiplier circuits

Solved: Chapter 18 Problem 17P Solution | Fundamentals Of Logic Design